八月_半導體專題|先進封裝技術在高性能運算晶片應用狀況剖析(中)

根據IEEE發布的異質整合技術發展藍圖報告指出,短期高性能計算晶片係以大面積中介層、嵌入式橋接載板、小孔徑比矽通孔、面對面晶片堆疊、混和鍵合等技術鏈結其他晶片,說明如下:

- 大面積中介層:是目前高性能計算晶片採用之5D封裝主流技術,通常透過中介層連結四顆高頻寬記憶體(HBM),隨著晶片性能不斷提升,將需要更大尺寸的中介層以容納八顆高頻寬記憶體。

- 嵌入式橋接層:是在載板中嵌入以矽或玻璃製作的橋接層,並透過兩側Pillar分別和晶片與載板鍵合以取代矽中介層。目前採用者有Intel的EMIB與日月光的FOCos-Bridge技術[詳細討論如前面文章:Chiplet 引發半導體革命技術 ]。當置入精度大幅提升後,預期載板可以嵌入多片橋接層以作為傳統5D封裝的替代方案。

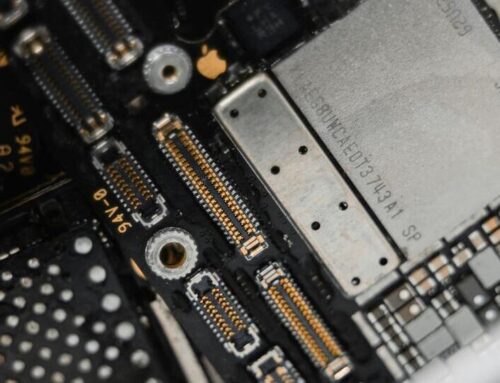

- 小孔徑矽通孔:目前矽中介層的矽通孔之深寬尺寸通常為100μm:10μm,堆疊的DRAM與邏輯晶片用矽通孔之深寬尺寸則分別是50μm:6μm、50μm:5μm,當3D封裝技術大量導入後,矽通孔須持續縮小以提升I/O點密度,目前已開發出直徑為1μm的矽通孔技術,但預估深寬比仍會維持10:1。

- 面對面晶片堆疊:目前頂部與底部晶片主要透過錫鉛製的Micro Bump鍵合,然而為提升I/O點密度,如Intel 的Foveros-Direct技術改用尺寸更小且更低電阻之銅製Pillar,可縮小接點間距至10μm。

- 混合鍵合:是將兩側晶片的金屬與氧化物混和介面直接貼合後以高溫讓金屬擴散鍵合。因為製程主要採用晶片製造設備,可減少接點間距至次微米等級,被視為實現真正3D封裝的關鍵技術。已廣泛用於CMOS影像感測器與邏輯晶片、記憶體鍵合,正導入高性能計算晶片封裝,如台積電的SoIC技術。

此外,該報告認為高性能計算晶片用先進封裝的中長期技術發展方向包括超細間距載板、無線晶片通信、矽光子解決方案,說明如下 :

更多詳細內容,請註冊會員或登入會員登入.