產業趨勢報告|Chiplet 引發半導體革命技術

Chiplet技術發展動能探討

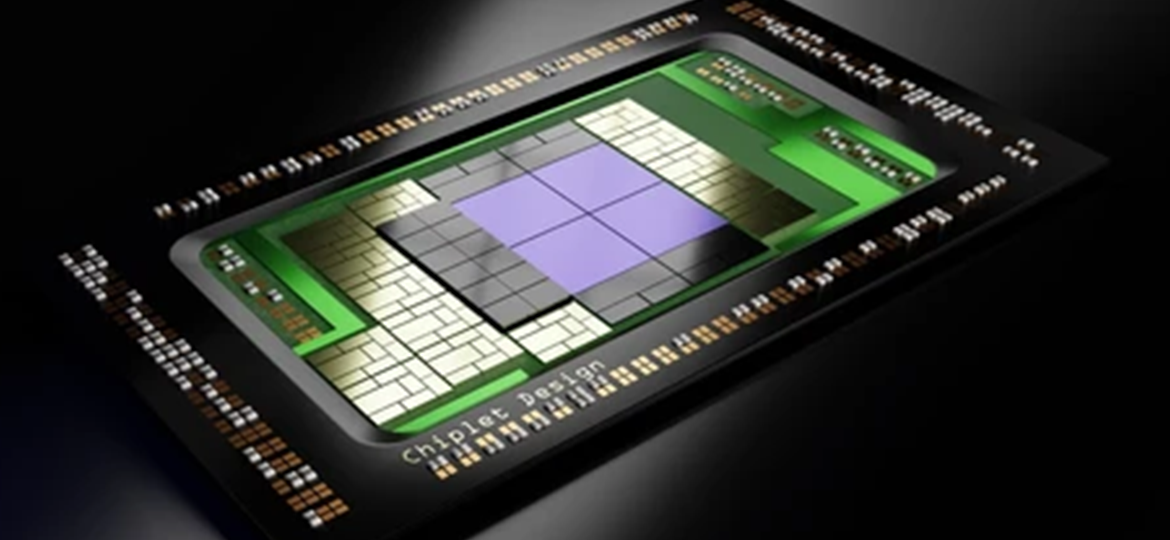

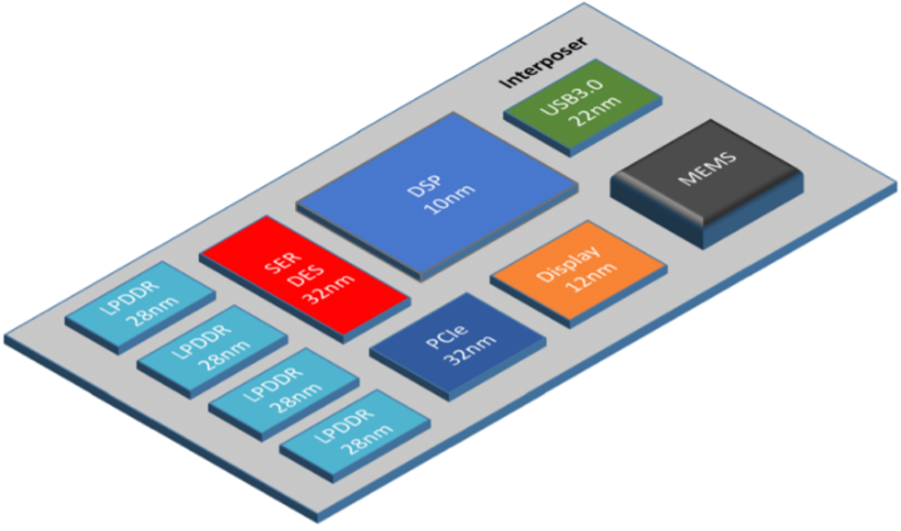

從前面的文章,我們論過在半導體電晶體中為降低功耗、提升效能,半導體製程持續推進,除了閘極寬度微縮外電晶體也從平面變成立體。然而生產成本也越墊越高,尤其半導體產業奉為圭臬的摩爾定律已逐漸失靈,無法透過製程微縮解決所有問題,因此Chiplet技術成為突破摩爾定律瓶頸、降低晶片開發與製造成本的解決方案,它是將單一晶片分割成如處理器、類比元件、記憶體等多個功能獨立小晶片,最後透過先進封裝整合為一顆功能完整晶片,如圖1所示。其概念源自於Intel共同創辦人Gordon Moore在1965年發表的論文《Cramming More Components Onto Integrated Circuits》,文中不僅提出著名的摩爾定律,同時也指出以單獨封裝和相互連接的單一功能小晶片去構建大型系統將更為經濟。2015 年Marvell 周秀文博士在國際固態電路研討會( ISSCC)上提出模組化晶片(MoChi)概念,使得半導體業界開始關注Chiplet技術,近幾年為了降低高階晶片的開發與製造成本,加上封裝技術突飛猛進,於是越來越多IC設計商導入Chiplet設計,成為重要的半導體技術發展趨勢,並正改變全球半導體產業生態。根據市場研究機構Omdia發布報告指出,預估全球Chiplet市場規模將從2024年的58億美元成長到2035年的570億美元。Chiplet技術具有以下三點的發展優勢 :

- 將 SoC進行Chiplet化後,每個Chiplet可分別選擇合適的製程技術製造,然後再透過先進封裝技術整合成單一SOC晶片,因而不需要採用前段先進製程,這樣可大幅降低晶片生產成本。

- 通常面積小的晶片缺陷少、晶圓面積利用效率佳,所以SoC進行Chiplet化後可大幅提高製程良率並降低生產成本。

- 將 SoC進行Chiplet化後能選擇性更新特定單元,藉此減少重複的設計和驗證工作,進而降低晶片設計的複雜度與成本,並縮短新產品開發時程。

圖1、Chiplet架構示意圖

資料來源 : Cadence